10+ sdram block diagram

Clock and Reset Interfaces 303. ARM9 CPU Block Diagram MNL162A100 Schema a Blocchi Block Diagram NAND FLASH 128MB SDRAM 64MB ETH USB HOST USB OTG DCDC 5-33Vdc 5Vdc VOUT33Vdc.

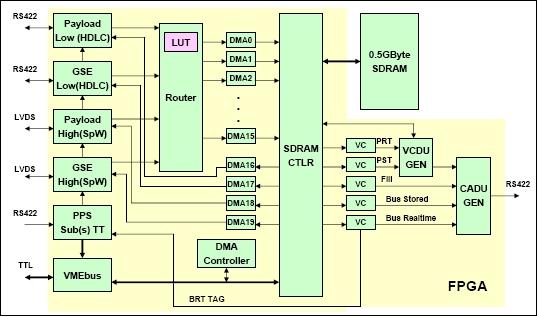

Tacsat 4

DDR3 SDRAM MT41J1G4 128 Meg x 4 x 8 banks MT41J512M8 64 Meg x 8 x 8 banks MT41J256M16 32 Meg x 16 x 8 banks Features V DD V DDQ 15V 0075V 15V center.

. SDRAM Controller Memory Options 124. SDRAM Controller Subsystem Block Diagram 123. Memory Controller Architecture 116.

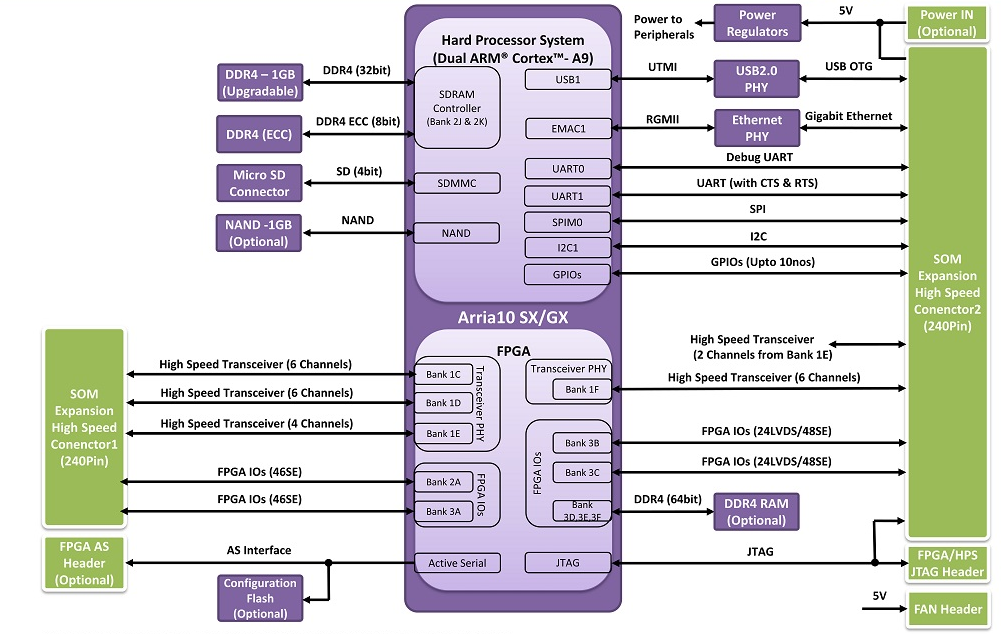

Terasic Stratix 10 SoC Board. Siemens AG Documentation Block Diagram 40 1 1412013 A5E31374985A 002EB200P Memories P. SDRAM Controller Subsystem Interfaces 115.

FPGA-to-HPS AXI Slave Interface 304. SRAM Die Size Efficiency DRAM is as much as 6x smaller in comparison to SRAM on a per bit basis. All the connections are established through the Arria 10 SoC FPGA device to provide maximum flexibility for users.

SDRAM Controller Subsystem Block Diagram 63. SDRAM Controller Memory Options 114. Remote System Update Compatibility Agilex SoC GSRD Agilex SoC Golden System Reference Design.

Design and Verification of SDRAM Controller Based on FPGA FPGA and Verification ResearchGate the professional. SDRAM Memory Controller Static RA M T ech nology 6T Memory Cell Memory Access Timin g Dynami c R A M Te chnolo gy 1T Memory Cell Memory Access Timin g CS 150 - Spring 2004. 017-024 018 - Level shifters 019 - Level shifters 020 - SDRAM - Micron 021 -.

At higher clock rates the useful CAS latency in clock cycles naturally increases. Functional Block Diagram 256 Meg x8 DDR3 SDRAM is a high-speed CMOS dynamic random access memory. Cell size for SRAM roughly 6x the size of a DRAM cell 6.

Users can configure the FPGA to. Memory Controller Architecture 66. SDR SDRAM MT48LC16M4A2 4 Meg x 4 x 4 Banks MT48LC8M8A2 2 Meg x 8 x 4 Banks MT48LC4M16A2 1 Meg x 16 x 4 Banks Features PC100- and PC133-compliant Fully.

SDRAM Controller Subsystem Interfaces 125. SDRAM L3 Interconnect Block Diagram and System. SDRAM Controller Subsystem Interfaces 65.

Document Table of Contents. Download scientific diagram SDRAM block diagram. Intel Stratix 10 Hard Processor System Technical Reference Manual.

CS150 Fall 2002 Project Report - 10 - Draw your block diagram for the SDRAM InterfaceFrame Buffer Manager showing the major pieces ieFSMs buffers FIFOs CL etc and their. SDR SDRAM MT48LC64M4A2 16 Meg x 4 x 4 banks MT48LC32M8A2 8 Meg x 8 x 4 banks MT48LC16M16A2 4 Meg x 16 x 4 banks Features PC100- and PC133-compliant Fully. The Micron128Mb SDRAM is a high-speed CMOS dynamic random-access memory containing 134217728 bits.

SDRAM Controller Memory Options 64. It is internally configured as an 8-bank DRAM Functional Block Diagram. HPS-to-FPGA AXI Master Interface 305.

LPDDR4LPDDR4X SDRAM MT53D512M16D1 MT53D512M32D2 MT53D1024M32D4 Features This data sheet is for LPDDR4 and LPDDR4X unified product based on LPDDR4X information. Much lower Cost DRAM vs. It is internally configured as a quad-bank DRAM with a synchronous interface.

Lightweight HPS-to-FPGA AXI Master Interface. 1015 ns is 23 cycles CL23 of the 200 MHz clock of DDR-400 SDRAM CL4-6 for DDR2-800 and CL8-12 for. Memory Controller Architecture 126.

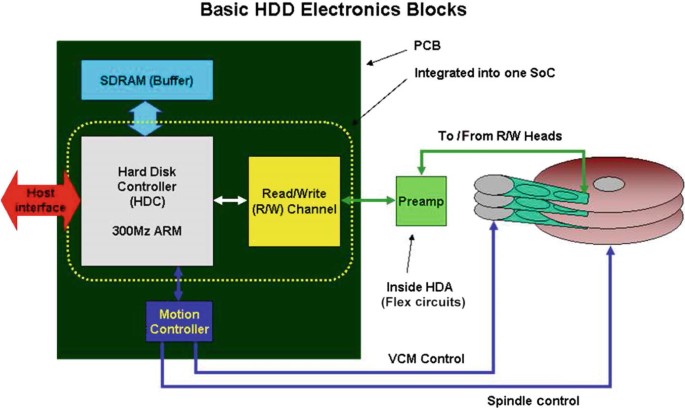

SDRAM Controller Subsystem Block Diagram 113. Top Level Block Diagram Team Member Responsibilities Brandon Ray App and Memory Jayme Lee Processor Power Fingerprint Scanner Jonathan Calderon LCD Wi-Fi Music Chris Shin. Figure 2-3 is the block diagram of the board.

Alinx Ax309 Xilinx Fpga Development Spartan6 Xc6slx9 Spartan 6 Advanced Kit Free Shipping Thanksbuyer

Intel Arria 10 Soc System On Modules Iwave Systems Mouser

Types Of Ram Random Access Memory Computer Memory Memories

How To Design A 4kx8 Bit Memory System By Using 1kx4 Bit Memory Chips Quora

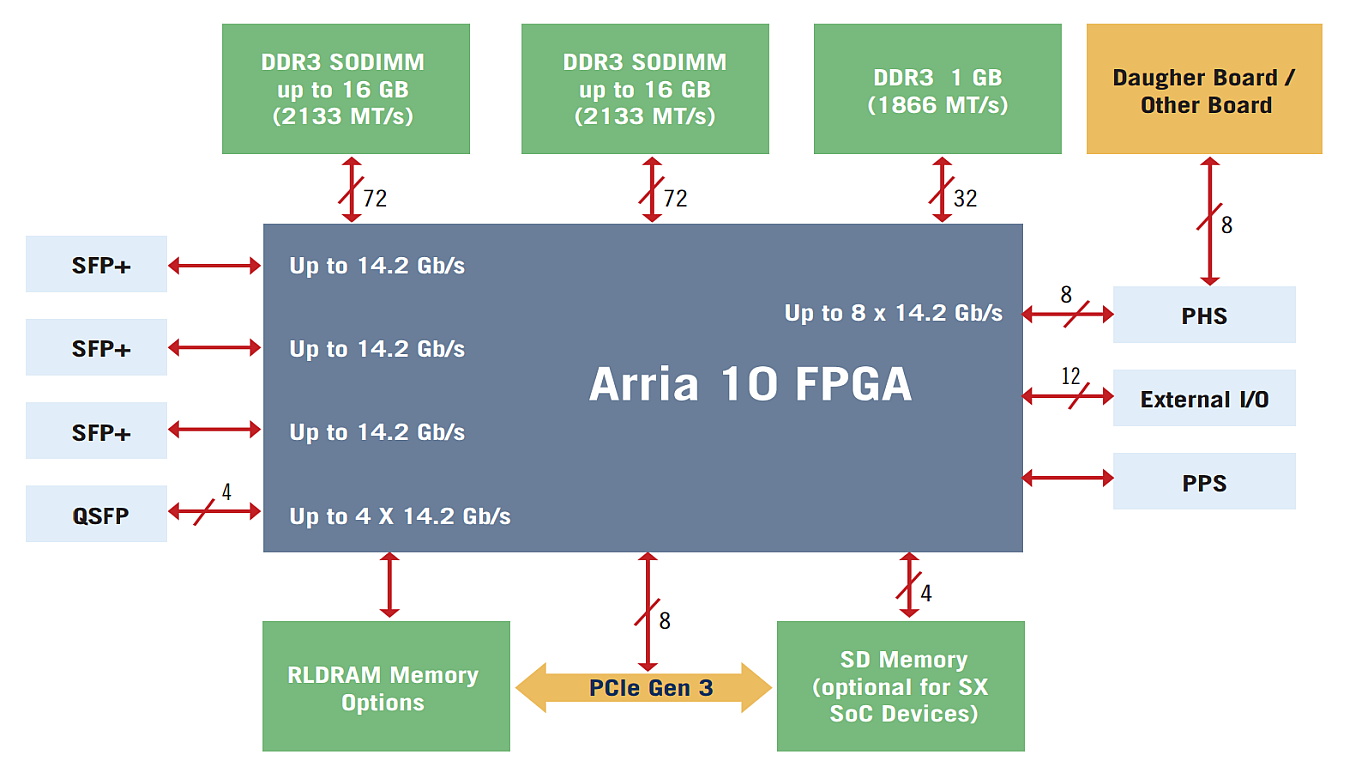

Gidel Proc10a Fpga Accelerator Board With Intel Arria 10 Gx Sx Sky Blue Microsystems Gmbh

Types Of Ram Random Access Memory Computer Memory Memories

Stm32f429zit6 Microcontroller Datasheet Reference Manual Pinout Faq

2

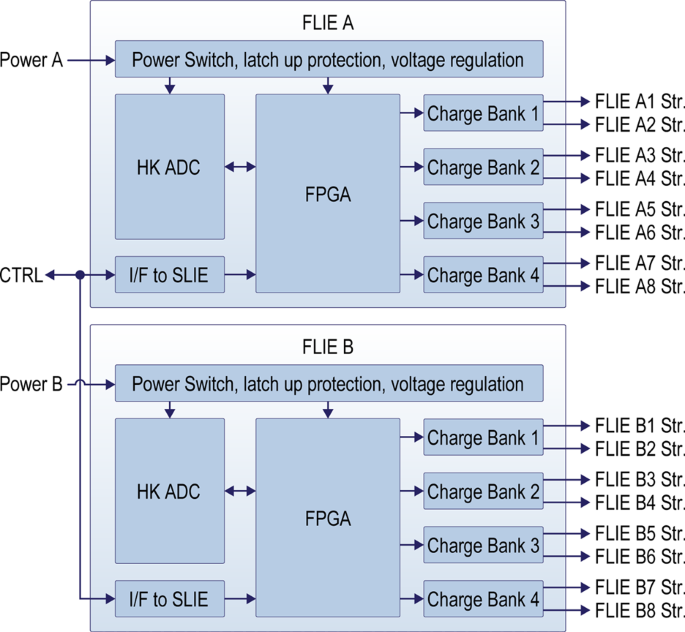

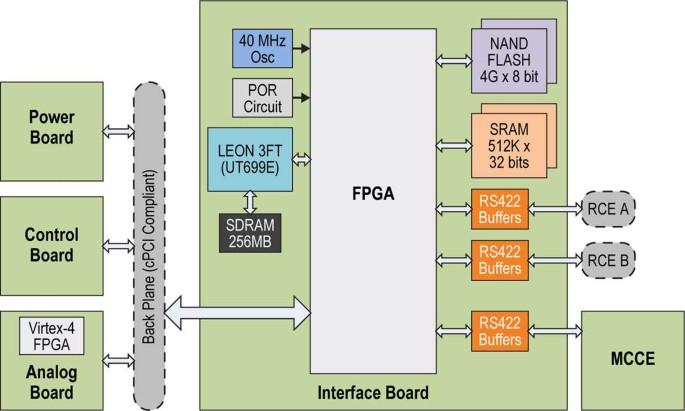

Pixl Planetary Instrument For X Ray Lithochemistry Springerlink

2

Is42s16400j 7tl Memory Cad Models Datasheet Features Video Faq

Delay Line Memory Wikiwand

Row Hammer Wikiwand

Introduction Springerlink

Pixl Planetary Instrument For X Ray Lithochemistry Springerlink

Memory Cell Computing Wikiwand

Memory Cell Computing Wikiwand